新型 3D 晶片制造技术,使电子产品更快、更节能

TechNews科技新报

2025年06月25号

作者 Emma stein

2025年06月25号

作者 Emma stein

麻省理工学院团队开发一种新制造方法,能以更低成本将高性能氮化镓电晶体无缝集成至标准矽 CMOS 晶片。

氮化镓(Gallium nitride,GaN)是仅次于矽的第二热门半导体材料,也是下一代高速通讯系统与先进数据中心所需电子设备关键,为了获得更高性能,科学家将 GaN 晶片与矽晶片相连,但焊接方法会限制 GaN 电晶体大小,若将整个 GaN 晶片整合至矽晶片,成本又非常高,因此商业化之路仍受限。

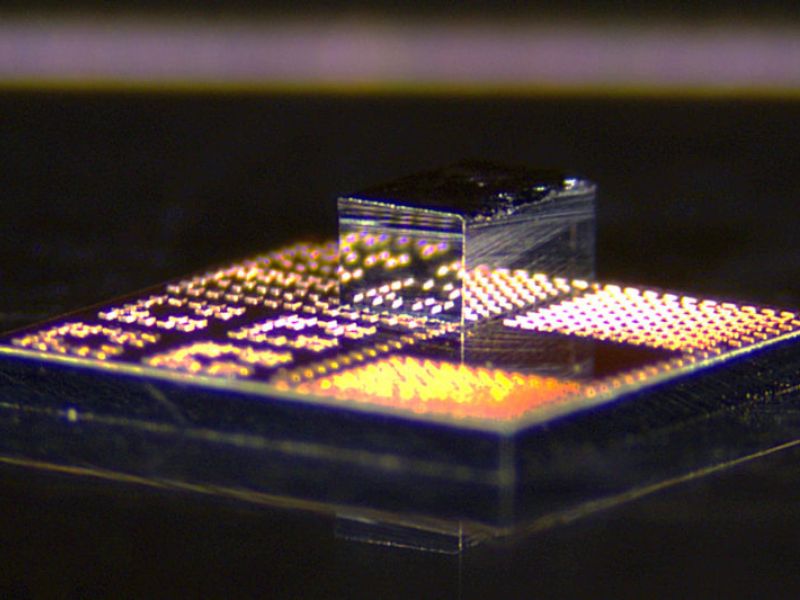

为解决此问题,麻省理工学院团队最近开发一种低成本、可扩展的 3D 积层新技术,能将高性能 GaN 电晶体集成至标准矽 CMOS 晶片,且与现有半导体制程兼容,突破现有 GaN 应用限制,促进高速通讯发展,并有望推动量子运算等前沿科技。

该方法首先在 GaN 晶片表面建置许多微小电晶体,接着以精细雷射技术将每个电晶体切成240 x 410 微米大小,每个电晶体顶部有微小铜柱,再于零下 400 ℃ 环境将一定数量电晶体黏合至矽晶片上,从而保留 2 种材料的功能并明显提升性能。

此外,GaN 电路由分散在矽晶片上的离散电晶体构成,还能降低整体系统温度。

研究团队利用此法开发功率放大器,成功实现比矽电晶体设备更高的讯号强度与效率,在智慧型手机中,这可以提高通讯品质,增加无线频宽,增强连接强度并延长电池寿命。

这项研究展示了多重氮化镓晶片与矽 CMOS 的三维整合能力,突破当前技术界限,有望带来速度更快、更节能的电子产品。

【免责声明】

本文章内容仅代表作者个人观点,与馗鼎无关。

内容性、文字阐述和原创性未经本站证实,对本文章及全部或部分内容、真实性、完整性、及时性本站不作任何保证或承诺,仅供读者参考,请自行核实相关内容。

馗鼎纳米科技股份有限公司 Creating Nano Technologies,Inc.

59 Alley 21 Lane 279, Chung Cheng Road, Yung Kang City, Tainan, TAIWAN

TEL:886-6-2323927 FAX:886-6-2013306 URL: http://www.creating-nanotech.com